5月9日,Advanced Materials(《先进材料》)在线发表了新葡萄88805官网何军教授课题组有关III-V族半导体制备的最新研究成果。文章题目为:“Van der Waals epitaxial growth of ultrathin indium antimonide on arbitrary substrates through low-thermal budget”。新葡萄88805官网为文章第一署名单位,何军教授、文耀副研究员为文章通讯作者,博士生熊自仁为第一作者。。

随着硅基晶体管技术不断发展,其功率密度提升面临瓶颈。将高迁移率材料(如III-V半导体,包括铟砷、铟镓砷和铟锑)集成到CMOS电路中成为一种有前景的解决方案。III-V半导体具备出色的物理特性,包括极高的迁移率、高频响应、探测灵敏度强以及优异发光特性等,使其在超越硅基电子器件应用中具有优势。然而,传统的III-V半导体异质外延受限于严格晶格、热以及极化匹配,并且其金属成分饱和蒸汽压较低,在制备过程中需要极端真空和高温条件,这阻碍了III-V半导体与柔性衬底以及硅基电路的原位兼容性。

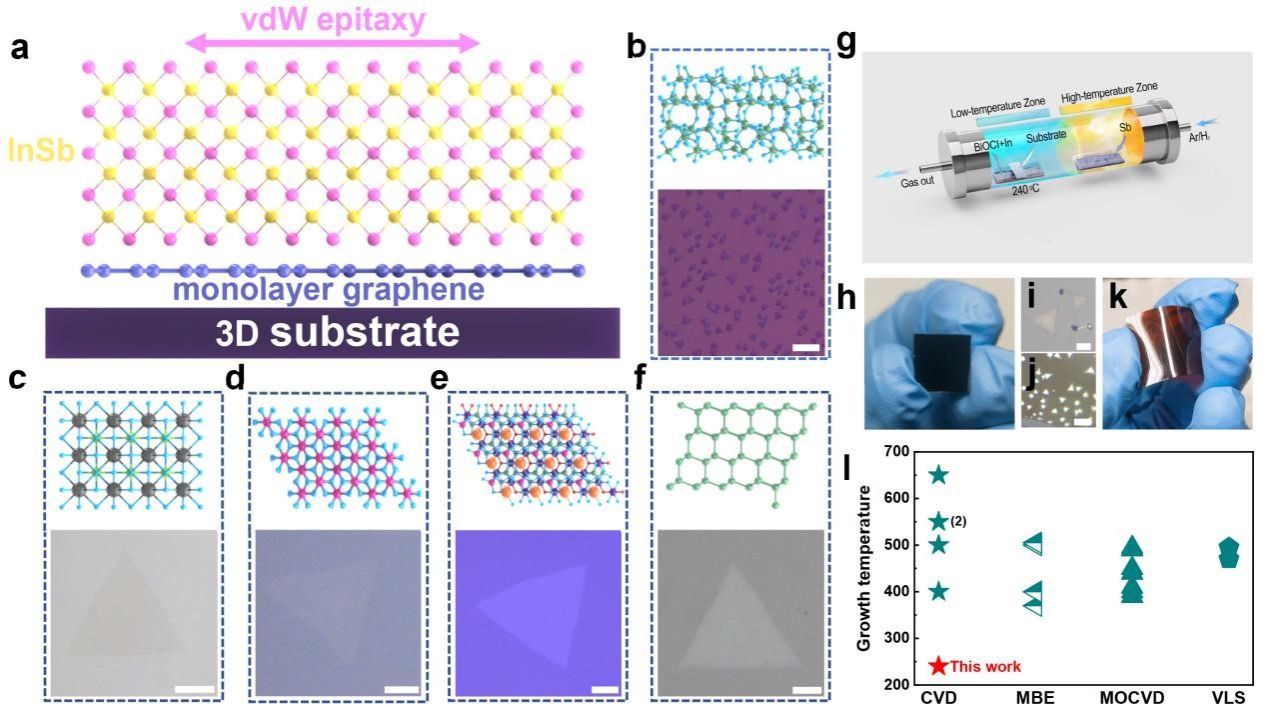

何军教授团队首次提出了一种新颖方法——采用低温范德华(vdW)外延技术,在多种衬底上成功制备了二维InSb单晶,其厚度仅2.4 nm。值得注意的是,在硅基衬底和柔性聚酰亚胺衬底上都实现了二维InSb原位生长。二维InSb生长所需温度(240°C)与微电子行业硅基集成后端工艺(<400°C)相兼容。基于二维InSb构建的场效应晶体管(FET)器件表现出108以上开/关比,并呈现出超低关态电流(小于10-13A)。此外,二维InSb展现p型输运行为,并且室温下场效应空穴迁移率达到203 cm2v-1s-1。这项研究为二维III-V半导体异质集成开辟了新的途径,并推动其在柔性电子领域中的应用发展,为调控二维尺度下的III-V半导体提供了平台,同时也为CMOS电路器件小型化开辟了一条新的路径。

该工作受到国家重点研发计划、国家自然科学基金等项目经费的支持。

原文链接:https://onlinelibrary.wiley.com/doi/10.1002/adma.202402435